# Designing and Implementation of BEC-1 using Reversible logic gate in QCA Technology

<sup>1</sup>Gyanesh Savita, <sup>2</sup>Namit Gupta <sup>1,2</sup>Shri Vaishnav Vidyapeeth Vishwavidyalaya, Indore, India

Orcid Id: 0009-0009-0992-406X, 0000-0001-6764-8467

Abstract— Quantum-dot cellular automata is an ideal computational model that offers lowered size, reduced energy consumption, higher speed, and deliberate design at nanometer scale. It was created as a solution to the scalability issue inherent in conventional Complementary Metal Oxide Semiconductor technologies. Coulomb repulsion is the foundation upon which the revolutionary nanotechnology known as QCA is built. On the nanoscale, the field of quantum computing has surfaced as a powerful model for the development of technology that is very effective in terms of energy consumption. In this article an Energy Efficient QCA based BEC-1 code Converter is proposed. It is designed by employing Feynman Gate and implemented in QCA Designer Tool. By optimizing its layout, BEC-1 has reduced the number of parameters to achieve efficiency, such as the cell count, space occupied in µm², 2.5 clock cycles latency, Average Energy dissipation in meV, Power dissipation in nano watt. According to the findings of the simulation, the proposed design functions without a single glitch and working as per its truth table and exhibits very little energy consumption.

Keywords—BEC-1, QCA, Reversible Logic gate, clocking in QCA, QCA designer tool, etc.

#### I. INTRODUCTION

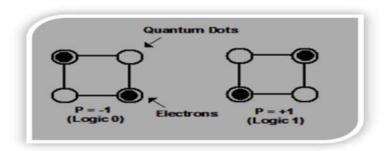

For the purpose of overcoming the constraints imposed by the scalability of Complementary Metal oxide Semiconductor based technology at the nanoscale, QCA is one of the best nanoelectronics technologies that is quickly expanding. It was proposed by ITRS, which stands for the International Technology Roadmap for Semiconductors. There were numerous alternative technologies for CMOS technology that were introduced by the ITRS; but, the QCA has been the most successful nanotechnology up until this point. A significant number of academics and researchers are working towards the actual implementation of QCA circuits in physical world. All QCA circuits are exclusively designed and built using software. Four quantum dots, one for each pair of electrons, make up the square that is the known as QCA Cell. Within the cell, the electrons have a propensity to find and arrange themselves in a diagonal pattern. The electrons undergo vertical shifts, either from the bottom to the top or vice versa, as a result of the tunnelling effect. However, they are unable to travel horizontally, either from the far left to the far right, because of Coulombic repulsion. Those electrons can't possibly be on the identical side due to their equal negative charge, causing them to migrate as

far away from each other as possible. As a result of the electric force acting opposingly on two electrons, two polarisation are created. Electrons located at the left top diagonal positions are denoted by logical value '0' (Polarisation -1). If the electrons are located at the bottom left diagonal positions, denoted by logical '1' (Polarisation +1). Both the polarization states are shown in Fig. 1. How much space a QCA circuit takes up and how long it takes to complete the process, are two factors that determine circuits cost [1], [2] and it is expressed in equation 1,

Circuit cost = circuit occupancy \* latency<sup>2</sup> .....equation (1)

## II NOTION OF QCA TECHNOLOGY

QCA based designs are initially created set up in a row of QCA cells, where every cell communicate electronic data to its neighboring cell [3]. The QCA-cell is crucial to the QCA method because it allows computation execution and information transmission within the cells, Bonding configurations involving pairs of electrons are present in every single cell. as depicted in Figure 1.

Fig. 1. The phenomenon of polarisation in QCA Cells [4]

Cell polarisation in QCA involves the creation of an electric field within a cell, that decides the binary value of cell either '1' or '0' as per its polrisation. It is possible to obtain QCA cells in two different initial states: the first state is composed of regular cells that are orientated at 90 degrees, and the second state is composed of cells rotated at 45 degrees. A cell with a 90-degree angle is shown in Figure 1 to have a polarization P = 1, is that is equal to 1 in binary [5]. On the other hand, a polarisation state with the value P = -1 is equivalent to the binary value 0. Previous research has shown that cells that are in a relaxed state continue to exist in a state that is not polarised throughout their lifetime [5], [6].

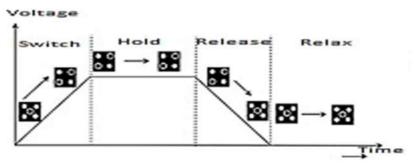

### III CLOCKING IN QCA

The QCA Clocking protocol allows for the creation and invalidation of the metastable stage. [7], [8]. In the QCA clocking action, there are four distinct stages: I-Switch, II-Hold, III-Release, and IV-Relax periods, indicated in Fig.2, When the I-phase (switch) is in progress, walls are raised, and the cells go through a process of polarisation that is

determined by the status of the cell adjacent to them. Barriers are maintained at a high level throughout the II-phase (Hold) so that the outputs can regulate the inputs of the stage. After this, the barriers are reduced during the III-Phase (Release), and the state of the cell becomes neutral. The Relaxed phase is characterised by the cell remaining in a non-polarized state. Four clocking zones, each 90 degrees out of phase with the others, are connected to the cells of a QCA.

Fig. 2 phases for QCA clocking [4]

#### IV ESSENTIAL CONCEPTS ASSOCIATED WITH REVERSIBLE LOGIC

- A. <u>Reversible Function</u>- If there are exactly as many outputs as there are inputs, we say that the Boolean function  $F(y_1; y_2,...y_m)$  is reversible. A distinct preimage is associated with each output pattern [9].

- B. <u>Reversible Logic</u>- In reversible logic, a one-to-one mapping can only be established when the number of inputs and the number of outputs of the gates are identical. For each set of input vectors, this method produces a unique set of output vectors. This lessens the impact of data loss, which in turn prevents power from dwindling. Because fan-out is not possible with reversible logic, several outputs cannot be tied to a single input. Additionally, feedback or loops are prohibited in reversible logic circuits. Key features of a reversible logic circuit include:

- (1) A limited number of input constants.

- (2) Required minimal quantity of reversible gates required.

- (3) Optimal Quantity of garbage outputs[9].

- C. <u>Garbage Output-</u> The additional outputs required to provide reversibility in an n-input-k-output function, also known as a (n;k) function, are referred to as garbage. When there is a need to have an equal number of i/p and o/p, more i/p or o/p can be added. The relationship between amount of garbage outputs and constant outputs hasbeen expressed as: "The sum of the input and a constant input equals the sum of the output and the

garbage" [9].

D. Quantum cost- known as the cost of the design in relation to the cost of a fundamental gate. It is possible to ascertain the number of fundamental binary reversal gate required to construct the design. Quantum cost is the cost of a circuit that can described using no more than two 2x2 unitary gates while maintaining a constant output. A 2x2 gate incurs the same quantum cost of one as a 1x1 gate, which is 0 [9].

### V REVERSIBLE LOGIC GATE

Reversible logic encompasses three primary design objectives.

- 1) In order to reduce the device's computational complexity, it is necessary to minimise the quantum cost[10]–[13].

- 2) The latency, which refers to the extent of complexity in the device, should be reduced to a minimum.

- 3) The additional i/p and unnecessary o/p that are not part of the gate's design and only exist to ensure the device may be reversed should be minimized and ideally removed entirely[14], [15].

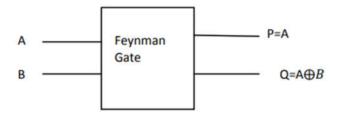

# VI FEYNMAN REVERSIBLE LOGIC GATE

A Feynman gate is the 2x2 gate, which is known as the controlled NOT gate. This gate is frequently utilized for fan-out reasons. Comprises the inputs (A, B) and the output P=A,  $Q=A\oplus B$  [16]–[18]. As depicted in Fig 3.

Fig. 3 Feynman Reversible Gate

Truth Table of Feynman Reversible Gate is depicted in fig. 4,

| Input |   | Output |   |  |

|-------|---|--------|---|--|

| A     | В | P      | Q |  |

| 0     | 0 | 0      | 0 |  |

| 0     | 1 | 0      | 1 |  |

| 1     | 0 | 1      | 1 |  |

| 1     | 1 | 1      | 0 |  |

Fig.4 Truth Table of Feynman Reversible Gate[18]

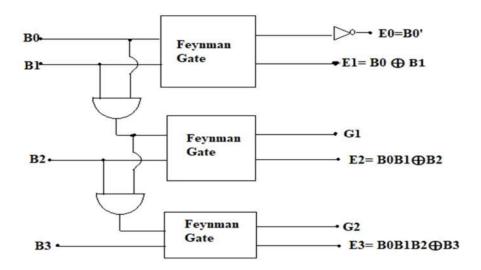

# VII BCD TO EXCESS-1 (BEC-1) CODE CONVERTER

BCD to Excess-1 code is very useful for Enhancing the speed of adder Circuit like Carry Select Adder, the main aim of using n-bit BEC-1 is to reduce the delay of addition. Simply adding one binary digit to the converting binary number is all that is needed to transform binary code to excess-1 code. In this case, we solely examined circuits that convert 4-bit binary to excess-1. [2], [19]–[23].

Fig.5. Logic Circuit of Proposed Reversible BEC-1

| В3 | B2 | <b>B</b> 1 | во | E3 | E2 | E1       | EO |

|----|----|------------|----|----|----|----------|----|

| o  | O  | O          | o  | O  | o  | 0        | 1  |

| O  | O  | O          | 1  | O  | 0  | 1        | O  |

| O  | O  | 1          | O  | O  | 0  | 1        | 1  |

| O  | O  | 1          | 1  | O  | 1  | O        | O  |

| O  | 1  | O          | O  | O  | 1  | 0        | 1  |

| O  | 1  | O          | 1  | O  | 1  | <b>1</b> | O  |

| O  | 1  | 1          | O  | 0  | 1  | 1        | 1  |

| O  | 1  | 1          | 1  | 1  | O  | O        | O  |

| 1  | O  | O          | O  | 1  | O  | 0        | 1  |

| 1  | O  | O          | 1  | 1  | 0  | 1        | O  |

| 1  | O  | 1          | O  | 1  | O  | 1        | 1  |

| 1  | O  | 1          | 1  | 1  | 1  | О        | O  |

| 1  | 1  | O          | O  | 1  | 1  | O        | 1  |

| 1  | 1  | O          | 1  | 1  | 1  | 1        | О  |

| 1  | 1  | 1          | O  | 1  | 1  | 1        | 1  |

| 1  | 1  | 1          | 1  | X  | X  | X        | X  |

Fig.6 Truth Table of BEC-1

As shown in Figure 5. Feynman Gate based BEC-1 is a 4x4 combinational Circuit. Its input is B3(MSB), B2, B1 and B0(LSB). The outputs are E3(MSB), E2, E1, and E0(LSB) and there are two Garbage output G1 and G2 as well. The o/p equations of BEC-1 can be written as:

$E3 = B0B1B2 \bigoplus B3$ ,

$E2 = B0B1 \bigoplus B2$ ,

$E1 = B0 \oplus B1$ ,

E0 = (B0)

In this context, the symbol · represents the logical AND operation, the symbol + represents the logical OR operation, and the symbol  $\bigoplus$  represents the logical XOR operation. This circuit has 3 Feynman Reversible Logic gates, one inverter and two AND gates, Figure 5 represent the conceptual diagram of the BEC-1 and Fig.6 shows the truth table of BEC-1 Code Converter.

# VIII IMPLEMENTATION OF PROPOSED BEC-1 USING REVERSIBLE LOGIC GATE IN QCA DESIGNER TOOL

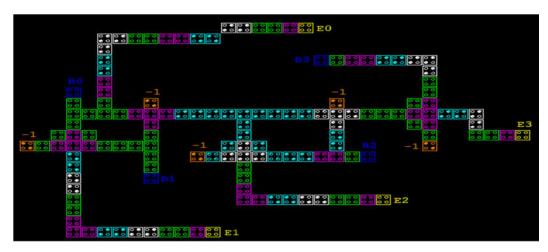

As shown in Fig.7, Proposed BEC-1 using Reversible logic gate is implemented and tested in QCA Designer tool and its functional verification is also done.

Fig.7 Implementation of Reversible BEC-1 in QCA Designer Tool

# IX RESULT AND SIMULATION WAVE FORM OF IMPLEMENTED BEC-1 CODE CONVERTER

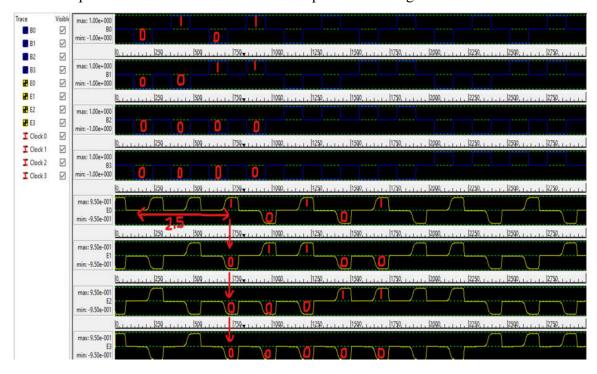

In Figure 8, Simulation waveform of Implemented BCD to Excess-1 Converter is shown, which depicts the functional verification of Implemented design.

Fig.8 Simulation Output waveform and functional verification of Proposed Reversible BEC-1 Code Converter

Simulation output of implemented BEC-1 Converter is depicted in Table 1.

| Circuit Design         | No.<br>of<br>Cells<br>used | Area<br>(μm²) | Latency<br>(Clock<br>cycles) | Average Energy<br>Dissipation/cycle<br>Eav | Power<br>Dissipation |

|------------------------|----------------------------|---------------|------------------------------|--------------------------------------------|----------------------|

| <b>Proposed BCD to</b> |                            |               |                              |                                            |                      |

| Excess1 (BEC-1)        | 141                        | 0.27          | 2.5                          | 4.43 meV                                   | 0.177 nW             |

#### VII PERFORMANCE PARAMETERS AND METHODOLOGY USED:

To evaluate the design efficacy of any architecture in QCA technology, five key characteristics must be considered: the number of cells, the area utilized in micrometers square (m<sup>2</sup>), delay in terms of clock cycles, Average Energy Consumption per cycle and power dissipation. The measuring of these qualities is made easier by the use of a simulation tool known as QCA designer 2.0.3 and QCA Designer E tool [24], [25]. A summary of these and other performance measures is as follows:

- 1) **Cell count:** The term "cell" refers to the total number of individual components used in the building of a circuit design. The proposed design exhibits a total cell count of 141, as depicted in Figure 7.

- 2) **Area Occupied:** "Area occupancy" is the measure of how cells are spatially utilized in a circuit. During the design phase, it is standard practice to place each individual cell at a distance of 2 nm from its next cell[4],[26], [27]. Furthermore, it is important to mention that the surface area occupied by a single cell is 324 nm2. The total area is determined by identifying all cells that possess a distinct gap between them. As shown in Figure 7, BEC-1 circuit design collectively occupies an area of 0.27 Micrometer<sup>2</sup>.

- 3) **Delay (Latency):** The computation is derived by multiplying 0.25 with the total number of clock phases employed in generating the required output. Proposed BEC-1, seen in Figure 7 employ maximum 10 clock phases to get the desired outcome. Therefore, the latency[28], [29] of the entity is calculated as 0.25 multiplied by 10, resulting in a value of 2.5.

- 4) **Average Energy Dissipation per Cycles**: Value of Average Energy Dissipation per cycle[30] in proposed design is 4.43 meV.

- 5) **Power Dissipation:** Value of Power Dissipation[31], [32] in proposed design is 0.177 nW.

## VIII SIMULATION FRAMWORK AND KEY CRITERIA

Simulation Framework and Key Criteria used to realize the circuit are mentioned in table 2.

Table 2. Simulation Framework and Key Criteria

| Parameters/key criteria  | Values                  |

|--------------------------|-------------------------|

| Radius of effect         | 0.065 μm                |

| Relative permittivity    | 12.9                    |

| Cell size                | 0.018 μm                |

| Cell area                | $0.324~\mu\text{m}^2$   |

| Separation gap           | 0.002 μm                |

| Overall samples          | 12000                   |

| Convergence tolerance    | 0.0000100               |

| Clock low                | 3.8x10 <sup>-23</sup> J |

| Clock shift              | 0                       |

| Clock high               | 9.8x10 <sup>-22</sup> J |

| Clock amplitude factor   | 2                       |

| Layer Separation         | 11.5                    |

| Maximum iteration/sample | 100                     |

# VII. CONCLUSION AND FUTURE SCOPE

Recent studies examining the development of nano-electronics circuitry have focused on nanotechnology. Since digital logic gates are the fundamental parts of all digital circuits, simpler, faster designs with the fewest possible zones are essential. This paper Proposed an Energy and Area Efficient BEC-1 design, in the QCA Designer tool for nano-scale

applications. The constructed BEC-1 has achieved an optimal layout with less cell count, area occupancy in  $\mu m^2$  and delay of only 2.5 clock cycles, average energy dissipation in **meV**, Power dissipation in **nano watt**. According to the execution parameters, the proposed design has the potential to be employed in designing and implementation of QCA based Energy Efficient Fast adders like RCA, CSLA, SQRT CSLA, Binary incrementor circuits to make efficient and speedy ALUs in future.

**Conflicts of Interest-** The Authors declare that they have no conflicts of interest in this work.

**Data Availability**- No data set has been used for this research paper.

#### References

- [1] H. Thapliyal, N. Ranganathan, and S. Kotiyal, "Design of testable reversible sequential circuits," *IEEE Trans. Very Large Scale Integr. Syst.*, vol. 21, no. 7, pp. 1201–1209, 2013, doi: 10.1109/TVLSI.2012.2209688.

- [2] A. Kaity and S. Singh, "Optimized area efficient quantum dot cellular automata based reversible code converter circuits: design and energy performance estimation," *J. Supercomput.*, vol. 77, no. 10, pp. 11160–11186, 2021, doi: 10.1007/s11227-021-03693-9.

- [3] M. Mustafa and M. R. Beigh, "Design and implementation of quantum cellular automata based novel parity generator and checker circuits with minimum complexity and cell count," *Indian J. Pure Appl. Phys.*, vol. 51, no. 1, pp. 60–66, 2013.

- [4] G. L. Snider *et al.*, "Quantum-dot cellular automata: Introduction and experimental overview," *Proc. IEEE Conf. Nanotechnol.*, vol. 2001-January, pp. 465–470, 2001, doi: 10.1109/NANO.2001.966467.

- [5] A. M. Chabi, S. Sayedsalehi, S. Angizi, and K. Navi, "Efficient QCA Exclusive-or and Multiplexer Circuits Based on a Nanoelectronic-Compatible Designing Approach," *Int. Sch. Res. Not.*, vol. 2014, no. d, pp. 1–9, 2014, doi: 10.1155/2014/463967.

- [6] S. Hashemi, M. Rahimi Azghadi, and K. Navi, "Design and analysis of efficient QCA reversible adders," *J. Supercomput.*, vol. 75, no. 4, pp. 2106–2125, 2019, doi: 10.1007/s11227-018-2683-0.

- [7] G. Singh, R. K. Sarin, and B. Raj, "A novel robust exclusive-OR function implementation in QCA nanotechnology with energy dissipation analysis," *J. Comput. Electron.*, vol. 15, no. 2, pp. 455–465, 2016, doi: 10.1007/s10825-016-0804-7.

- [8] S. Husain and N. Gupta, "e-Prime Advances in Electrical Engineering, Electronics and Energy Enhancing fault tolerance in QCA-based RAM cells: A USE clock-driven approach with a novel majority voter," *e-Prime Adv. Electr. Eng. Electron. Energy*, vol. 6, no. October, p. 100352, 2023, doi: 10.1016/j.prime.2023.100352.

- [9] P. Biswas, N. Gupta, and N. Patidar, "Basic Reversible Logic Gates and It's Qca Implementation," *J. Eng. Res. Appl. www.ijera.com*, vol. 4, no. 6, pp. 12–16, 2014, [Online]. Available: www.ijera.com

- [10] A. Roy et al., "A Novel Design of Reversible Gate using Quantum-Dot Cellular Automata (QCA)," 2020 IEEE Int. Conf. Converg. Eng. ICCE 2020 Proc., pp. 110–115, 2020, doi:

- 10.1109/ICCE50343.2020.9290583.

- [11] A. Naghibzadeh and M. Houshmand, "Design and simulation of a reversible ALU by using QCA cells with the aim of improving evaluation parameters," *J. Comput. Electron.*, vol. 16, no. 3, pp. 883–895, 2017, doi: 10.1007/s10825-017-1004-9.

- [12] Y. Syamala and A. V. N. Tilak, "Reversible arithmetic logic unit," *ICECT 2011 2011 3rd Int. Conf. Electron. Comput. Technol.*, vol. 5, pp. 207–211, 2011, doi: 10.1109/ICECTECH.2011.5941987.

- [13] A. N. Bahar, F. Ahmad, S. Wani, S. Al-Nisa, and G. M. Bhat, "New modified-majority voter-based efficient QCA digital logic design," *Int. J. Electron.*, vol. 106, no. 3, pp. 333–348, 2019, doi: 10.1080/00207217.2018.1531315.

- [14] L. Jamal and H. M. H. Babu, "Design and implementation of a reversible central processing unit," *Proc. IEEE Comput. Soc. Annu. Symp. VLSI, ISVLSI*, vol. 07-10-July, pp. 187–190, 2015, doi: 10.1109/ISVLSI.2015.74.

- [15] A. K. Thakre, S. S. Chiwande, and S. D. Chafale, "Design of low power multiplier using reversible logic gate," *Proceeding IEEE Int. Conf. Green Comput. Commun. Electr. Eng. ICGCCEE 2014*, 2014, doi: 10.1109/ICGCCEE.2014.6922303.

- [16] P. K. Biswas, A. N. Bahar, M. A. Habib, and M. Abdullah-Al-Shafi, "Efficient Design of Feynman and Toffoli Gate in Quantum dot Cellular Automata (QCA) with Energy Dissipation Analysis," *Nanosci. Nanotechnol.*, vol. 7, no. 2, pp. 27–33, 2017, doi: 10.5923/j.nn.20170702.01.

- [17] S. Riyaz and V. Kakkar, "Quantum-dot Cellular Automata: An Efficient and Adroit Alternate to CMOS Technology," *2020 Int. Conf. Emerg. Smart Comput. Informatics, ESCI 2020*, pp. 282–288, 2020, doi: 10.1109/ESCI48226.2020.9167618.

- [18] M. Abdullah-Al-Shafi, M. Shifatul, and A. Newaz, "A Review on Reversible Logic Gates and its QCA Implementation," *Int. J. Comput. Appl.*, vol. 128, no. 2, pp. 27–34, 2015, doi: 10.5120/ijca2015906434.

- [19] M. Saravanan and K. S. Manic, "Energy efficient code converters using reversible logic gates," 2013 Int. Conf. Green High Perform. Comput. ICGHPC 2013, pp. 1–6, 2013, doi: 10.1109/ICGHPC.2013.6533921.

- [20] C. Mukherjee, S. Panda, A. K. Mukhopadhyay, and B. Maji, "QCA Gray Code Converter Circuits Using LTEx Methodology," *Int. J. Theor. Phys.*, vol. 57, no. 7, pp. 2068–2092, 2018, doi: 10.1007/s10773-018-3732-4.

- [21] L. Mugilvannan and S. Ramasamy, "Low-power and area-efficient carry select adder using modified BEC-1 converter," 2013 4th Int. Conf. Comput. Commun. Netw. Technol. ICCCNT 2013, pp. 1–5, 2013, doi: 10.1109/ICCCNT.2013.6726499.

- [22] R. B. S. Kesava, B. L. Rao, K. B. Sindhuri, and N. U. Kumar, "Low power and area efficient Wallace tree multiplier using carry select adder with binary to excess-1 converter," *Conf. Adv. Signal Process. CASP 2016*, pp. 248–253, 2016, doi: 10.1109/CASP.2016.7746174.

- [23] P. Nautiyal, P. Madduri, and S. Negi, "Implementation of an ALU using modified carry select adder for low power and area-efficient applications," *2015 Int. Conf. Comput. Comput. Sci. ICCCS 2015*, pp. 22–25, 2015, doi: 10.1109/ICCACS.2015.7361316.

[24] A. Yan *et al.*, "Designs of BCD Adder Based on Excess-3 Code in Quantum-Dot Cellular Automata," *IEEE Trans. Circuits Syst. II Express Briefs*, vol. 70, no. 6, pp. 2256–2260, 2023, doi: 10.1109/TCSII.2023.3237695.

- [25] S. Aralikatti, "QCA Designer: A simulation and Design Layout Tool for QCA based Nano Domain Computing Architectures," *Proc. 2nd Int. Conf. Inven. Res. Comput. Appl. ICIRCA* 2020, pp. 1042–1046, 2020, doi: 10.1109/ICIRCA48905.2020.9183046.

- [26] S. Perri, F. Spagnolo, F. Frustaci, and P. Corsonello, "Multibit Full Comparator Logic in Quantum-Dot Cellular Automata," *IEEE Trans. Circuits Syst. II Express Briefs*, vol. 69, no. 11, pp. 4508–4512, 2022, doi: 10.1109/TCSII.2022.3193561.

- [27] A. Moustafa and A. Younes, "Efficient Synthesis of Reversible Circuits Using Quantum Dot Cellular Automata," *IEEE Access*, vol. 9, pp. 76662–76673, 2021, doi: 10.1109/ACCESS.2021.3083507.

- [28] B. Basheer and R. M. Varkey, "Review on various full adder circuits," *Proc. 3rd Int. Conf. Comput. Methodol. Commun. ICCMC 2019*, no. Iccmc, pp. 877–880, 2019, doi: 10.1109/ICCMC.2019.8819680.

- [29] B. Raina, C. Verma, M. Gupta, and V. K. Sharma, "Binary Coded Decimal (BCD) Seven Segment Circuit Designing using Quantum-dot Cellular Automata (QCA)," *Proc. 5th Int. Conf. Trends Electron. Informatics, ICOEI 2021*, pp. 126–130, 2021, doi: 10.1109/ICOEI51242.2021.9453046.

- [30] M. Patidar and N. Gupta, "An efficient design of edge-triggered synchronous memory element using quantum dot cellular automata with optimized energy dissipation," *J. Comput. Electron.*, vol. 19, no. 2, pp. 529–542, 2020, doi: 10.1007/s10825-020-01457-x.

- [31] N. Safoev, G. Abdukhalil, and K. A. Abdisalomovich, "QCA based Priority Encoder using Toffoli gate," *14th IEEE Int. Conf. Appl. Inf. Commun. Technol. AICT 2020 Proc.*, 2020, doi: 10.1109/AICT50176.2020.9368637.

- [32] S. Babaie, A. Sadoghifar, and A. N. Bahar, "Design of an Efficient Multilayer Arithmetic Logic Unit in Quantum-Dot Cellular Automata (QCA)," *IEEE Trans. Circuits Syst. II Express Briefs*, vol. 66, no. 6, pp. 963–967, 2019, doi: 10.1109/TCSII.2018.2873797.